ARM/POWER Relaxed Memory Model

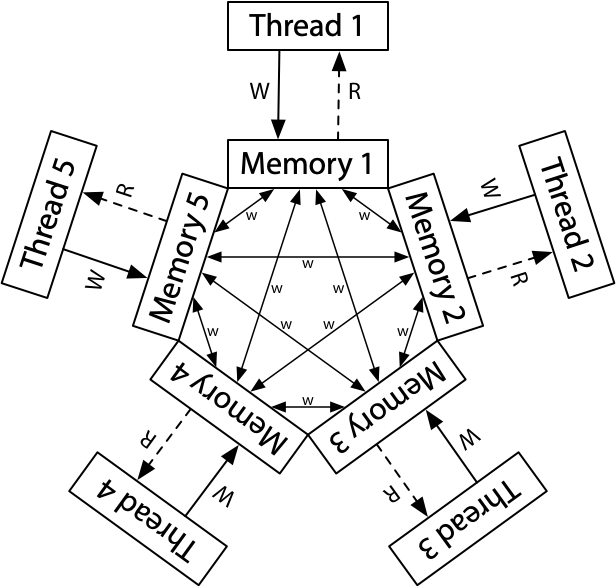

ARM和POWER系统的概念模型是,每个处理器从其自己的完整内存副本中读取和向其写入,每个写入独立地传播到其他处理器,随着写入的传播,允许重新排序。

在这个宽松的(relaxed)模型中,我们迄今为止所看到的每一个litmus test的答案都是“yes,这真的可能发生。”

Litmus Test: Message Passing

Can this program see r1 = 1, r2 = 0?

// Thread 1 // Thread 2

x = 1 r1 = y

y = 1 r2 = x

On sequentially consistent hardware: no.

On x86 (or other TSO): no.

On ARM/POWER: yes!

Litmus Test: Store Buffering

Can this program see r1 = 0, r2 = 0?

// Thread 1 // Thread 2

x = 1 y = 1

r1 = y r2 = x

On sequentially consistent hardware: no.

On x86 (or other TSO): yes!

On ARM/POWER: yes!

Litmus Test: Independent Reads of Independent Writes (IRIW)

Can this program see r1 = 1, r2 = 0, r3 = 1, r4 = 0?

(Can Threads 3 and 4 see x and y change in different orders?)

// Thread 1 // Thread 2 // Thread 3 // Thread 4

x = 1 y = 1 r1 = x r3 = y

r2 = y r4 = x

On sequentially consistent hardware: no.

On x86 (or other TSO): no.

On ARM/POWER: yes!

Litmus Test: Load Buffering

Can this program see r1 = 1, r2 = 1?

(Can each thread's read happen after the other thread's write?)

// Thread 1 // Thread 2

r1 = x r2 = y

y = 1 x = 1

On sequentially consistent hardware: no.

On x86 (or other TSO): no.

On ARM/POWER: yes!